Two years ago we kicked off our commitment to open-source innovation by announcing our goal to transition over one billion cores per year to RISC-V. As a founding member of the 150+ organization-strong RISC-V Foundation, our commitment hasn’t wavered and we’re proving it at the RISC-V Summit 2019. From new announcements about technical innovations to keynotes including Martin Fink’s Unshackling Memory, which discussed how today’s compute platforms have evolved and how RISC-V is a platform for memory to be freed from a processor. Look for a recording of that keynote in the days to come right here.

The annual, multi-day RISC-V Summit features presentations on a wide variety of technology topics and celebrates the dramatic growth and innovation brought forth by the RISC-V movement this year, and as it grows into the future.

Three technology announcements

• World’s first commercial dual-threaded embedded RISC-V core

• OmniXtend™ ecosystem and reference design

• Commercial support for SweRV Core™ EH1

Our open sourced RISC-V-based SweRV Core family is growing by two as we announce the world’s first commercial dual-threaded embedded core, SweRV Core EH2, and the company’s smallest SweRV Core to date, EL2. Plus, there’s a new hardware reference design for OmniXtend, the direct to caches over Ethernet fabric protocol. All SweRV Cores and OmniXtend designs will be further developed in the open collaborative CHIPS Alliance organization. We’re also making it even easier for the ecosystem to implement RISC-V technologies into devices, with the availability of hardware implementation packages and technical support for the SweRV Core EH1 through Codasip GmbH.

• SweRV Core EH2: The industry’s first multi-threaded, embedded core, SweRV Core EH2 supports the running of two simultaneous threads on top of its two-way superscalar architecture, enabling 6.3 Coremarks/Mhz performance in simulations. The design includes doubling of fetch buffers, instruction buffers, commit logic and other microarchitecture enhancements. This innovation may make it possible to reduce the number of CPUs in a device and adds further flexibility to the data-centric architecture. Like SweRV Core EH1 (formerly referred to as SweRV Core 1.1) introduced early this year, EH2 is a 32-bit, 9 stage pipeline core and is ideal for use in embedded devices designed for data-intensive artificial intelligence (AI), storage controllers and Internet-of-Things (IoT) applications.

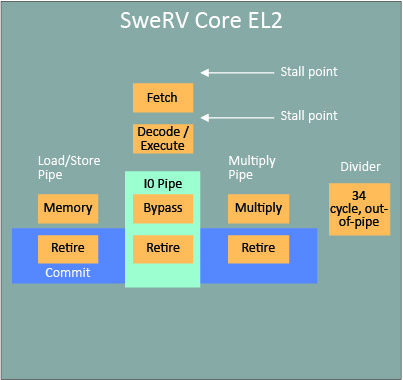

• SweRV Core EL2: At dimensions of .023mm @ 16nm, this ultra-small 3.6 Coremarks/Mhz (simulated)4-stage pipe is designed to replace sequential logic and state machines in controller SoCs.

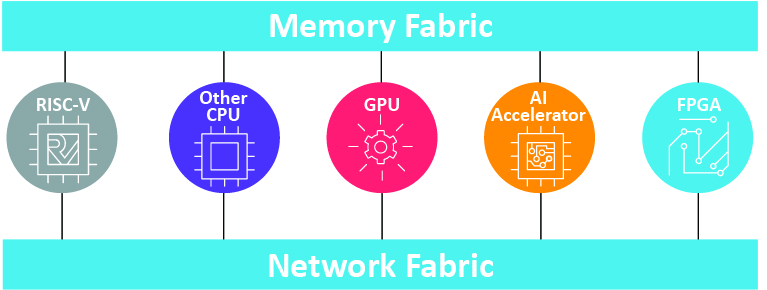

• CHIPS Alliance Broadens Support of Western Digital RISC-V innovations: Western Digital’s OmniXtend memory-centric system architecture is now managed by CHIPS Alliance project, which is hosted by the Linux Foundation. OmniXtend is an open approach to providing cache coherent memory over an Ethernet fabric. It leverages ubiquitous Ethernet for equally sharing main memory across processors, machine learning accelerators, GPUs, FPGAs and other components. Western Digital has contributed a hardware reference design that can be used to implement and test OmniXtend solutions. CHIPS Alliance support enables the ecosystems to further contribute, collaborate, develop and implement OmniXtend. CHIPS Alliance began managing Western Digital’s SweRV Core portfolio earlier this year.

• For commercial organizations that want to incorporate the SweRV Core EH1 in their designs, Western Digital has partnered with Codasip for design support and services. The new SweRV Support Package (SSP) from Codasip provides all of the components necessary to design, implement, test, and write software for a SweRV Core-based system-on-chip. This includes verification testbenches and IP, reference scripts for leading EDA flows, models for simulations, software development tools and more – all backed by professional support.

Learn more

Visit our RISC-V page for an in-depth view.

Download the Technical Brief for detailed info on all of today’s announcements.

Western Digital is a strong proponent and promoter of open source, both in open-source hardware, including RISC-V cores, and also in the software domain, where we participate and contribute to development of the Linux® kernel in areas related to our storage business. Visit Innovation at Western Digital for more.