Opening Doors to Open-Source Hardware, Software and Standards

In my presentation at Storage Field Day 19, I highlighted how we’re leading open source initiatives to improve storage performance and lower TCO for our hyperscale users. Data centers are growing in scale, thanks to new demands from AI, ML, IoT, and more. Our role is to make sure that the underlying data infrastructure is cost-effective and efficient. To this end, we’ve worked within the open source ecosystem to rethink hardware interfaces, along with the operating system and application software stack.

In this blog post, I’ll explain how our leadership in open-source hardware, software, and standards is driving new system architectures. To learn more, watch my full talk from Storage Field Day 19 below:

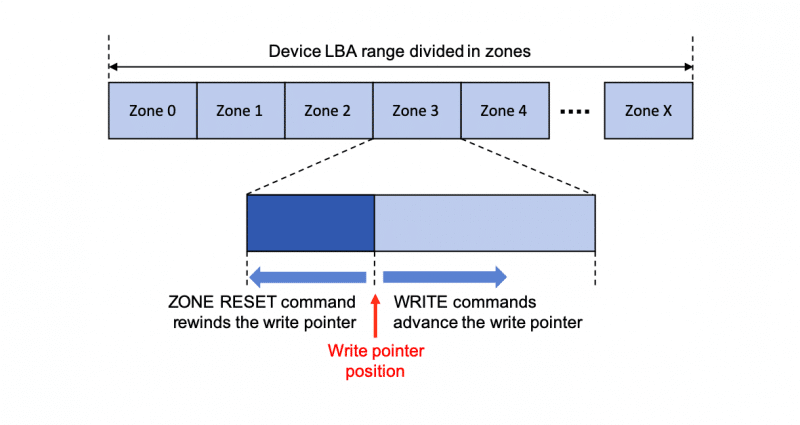

Zoned Storage, an Open Infrastructure, Unifies HDDs and SSDs

You might have seen our announcement of Zoned Storage, an open data infrastructure designed to support today’s data-driven world. But, if you haven’t, here’s what you need to know. It all starts with Zoned Storage Devices (ZSDs), which use “zones”, or designated address spaces that obey certain rules. During writes, data must start from the beginning of the zone and be written sequentially. Reading data is done in a similar fashion to traditional storage devices.

ZSDs use open standards to implement Zoned Storage, depending on the type of drive. Our enterprise HDDs use shingled magnetic recording (SMR), where data is placed in zones of overlapped tracks – much like a shingled roof. SMR is standardized for SAS as Zoned Block Commands (ZBC) and for SATA as Zoned Device ATA Command Set (ZAC). Similarly, our enterprise SSDs use the concept of “zoned namespaces” (ZNS) to enable intelligent data placement at the application level, instead of device level. ZNS is currently in the process of being standardized. We’ve proud to have contributed these standards directly to the Linux kernel, in addition to integration with applications and utilities that support zoned block devices.

Accelerating Open-Source Processor Innovation

As a leading data infrastructure company, we’ve been hard at work on open source hardware and software for compute architectures. RISC-V, an open instruction set architecture, is one such initiative that we’ve been leading. And, we’re proud to have been there since the beginning as a Founding Platinum member of the RISC-V Foundation – now at over 200 member companies strong. Since then, our involvement has included multiple global summits, hackathons, meetups, and more to help grow the RISC-V ecosystem.

We are using RISC-V to promote open standard interfaces and to accelerate innovation in our devices. To assist in this transformation, we’ve developed a line of three RISC-V SweRV™ cores that will soon be used in our products: the SweRV Core EH1, EH2, and EL2. All three cores are 32-bit, with various stages of pipelines, threads, and power-to-performance ratios. We collaborated with the CHIPS Alliance – an open source consortium that develops hardware for interfaces, processors, and systems – to make our SweRV cores open to the general public. Future SweRV cores will be developed in the CHIPS Alliance organization. You can learn more about our processor innovation on our RISC-V innovation page.

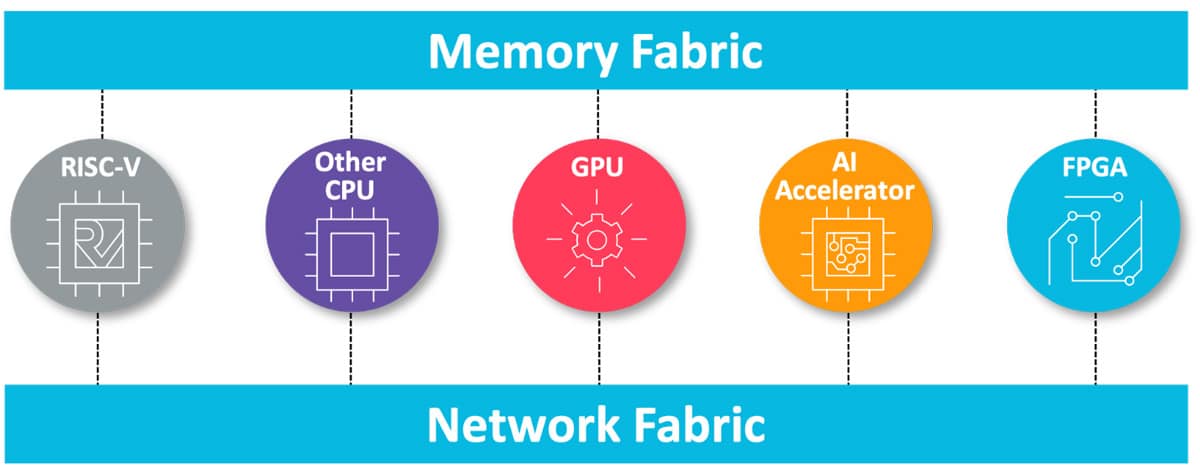

Open Source Enables Shared Memory Pools

It’s a story that we’ve seen time and again: enterprise systems have applications that compete over limited storage and compute resources. This competition creates bottlenecks in network speeds and potentially cause disruptions in accessibility and usability. To help address this issue, we again turned to open-source – a hardware reference design, in fact.

We call it OmniXtend. This memory fabric uses disaggregation via Ethernet to create shared pools of memory. In a multi-core system, this separation enables each core to have equal access to all the memory available in a single address space. This open-source protocol uses cache coherency to resolve conflicts when multiple cores – each with their own cache – read from or write to a shared memory space. As an open standard, cache coherency fabric, OmniXtend can be extended via Ethernet to multiple processors, GPUs, FPGAs, AI accelerators, and more. To learn more about OmniXtend, visit www.westerndigital.com/risc-v or see the latest technical details at the CHIPS Alliance github: https://github.com/chipsalliance

Protecting Data Infrastructure through Open Source Security

Data privacy should never take a backseat when designing data centers. That’s why we turned to open source to enable open, inspectable, and secure data infrastructure. We’re proud to be a founding partner of OpenTitan, an open-source, silicon project. It’s the first-of-its-kind to pursue building a transparent, high-quality reference design for silicon root-of-trust (RoT) chips. As I mentioned in my previous blog post, a RoT is “a set of functions in a computing module that is always trusted by the computer’s operating system (OS).” Essentially, this RoT helps validate integrity of multiple elements across a complex system, including the initial boot firmware.

We are excited about the possibilities that OpenTitan offers for data privacy and security, and are committed to the project in the long-term. While today we are focused on the reference chip design, the future holds opportunities for derived embedded IP, security models, and integration architectures necessary to incorporate OpenTitan into the heart of our disk controllers.

Open Up to Our Open Source Initiatives

- Find out how we are migrating to 1 billion RISC-V cores across our portfolio

- Learn how Dropbox built its in-house cloud platform using our SMR drives

- See how we’re using zoned storage for scalability in the Zettabyte Age